A few weeks ago, in what seems to be a truly modern phenomenon, I became aware that it was my third anniversary of joining Violin after I noticed a number of people congratulating me on LinkedIn. In many ways it feels like I've already been here for a lifetime, but it was only twelve months ago … Continue reading Postcards from Storageland: Three Years At Violin

Category: Flash

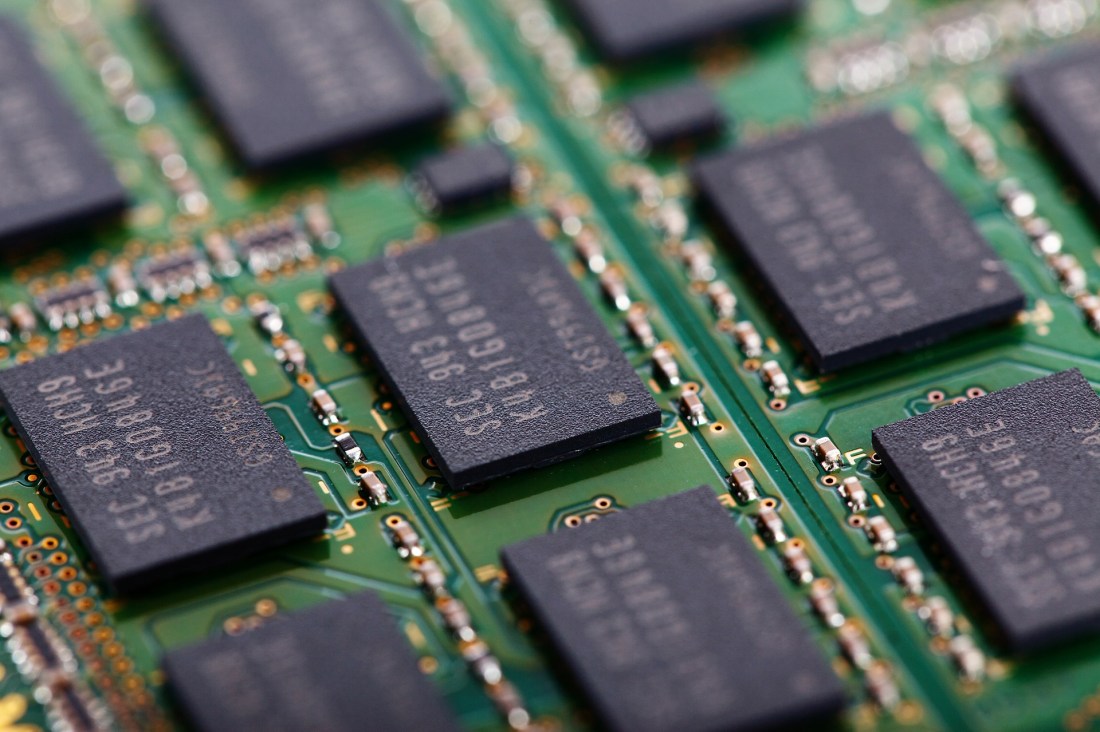

Understanding Flash: Fabrication, Shrinkage and the Next Big Thing

NAND flash manufacturers have been shrinking transistors for decades, but 2D planar NAND is hitting its physical limits. This article explains process geometries, 3D NAND as the answer, and why new memory technologies face a billion-dollar barrier to market.

Understanding Flash: Floating Gates and Wear

NAND flash wears out because repeated program and erase operations degrade the oxide layer in floating gate transistors. This article explains how flash cells store data and why wear affects SLC, MLC and TLC differently.

New Cookbook: Oracle Linux 6 Update 5 within an Oracle VM Template

I've posted a new installation cookbook for using Oracle within a virtual machine running on Oracle VM. Surprisingly, I was unable to come up with a satisfactory method of accessing external storage that did not involve the use of Oracle ASMLib... Oracle Linux 6 Update 5 within an Oracle VM Template

Understanding Flash: Unpredictable Write Performance

Not all NAND flash writes are equal. MLC flash has fast pages and slow pages, creating unpredictable write latency unless the storage controller manages them intelligently. This article explains why write performance varies and what enterprise arrays do about it.

Understanding Flash: The Write Cliff

When flash garbage collection cannot keep pace with incoming writes, performance falls off a cliff. This article explains background versus active garbage collection, write amplification and why predictability matters more than peak speed.

Postcard from Oracle OpenWorld 2014: The Oracle FS1 Flash Array

A couple of weeks ago I wrote a post about my trip to Oracle OpenWorld 2014 and the surprise announcement of the Oracle FS1 Flash Array. I posted it on the Violin Memory corporate website here: http://www.violin-memory.com/blog/postcard-oracle-openworld-2014-the-oracle-fs1-flash-array/ Follow the link to find out whether I thought it was the most amazing product in the history … Continue reading Postcard from Oracle OpenWorld 2014: The Oracle FS1 Flash Array

Understanding Flash: Garbage Collection Matters

NAND flash can only be erased at the block level, not the page level. Garbage collection is the process that recycles stale pages to keep a flash system writable – and without it, performance collapses. This article explains why.

Understanding Flash: The Flash Translation Layer

The flash translation layer is the hidden software layer that makes NAND flash usable as enterprise storage. This article explains logical block mapping, wear levelling, garbage collection and write amplification.

Oracle, Parallelism and Direct Path Reads… on Flash

Guest Post This is another guest post from my buddy Nate Fuzi, who performs the same role as me for Violin but is based in the US instead of EMEA. Because he's an American, Nate believes that "football" is played using your hands and that the ball is actually egg-shaped. This is of course ridiculous, … Continue reading Oracle, Parallelism and Direct Path Reads… on Flash