What's the most important attribute to consider when you want to buy a new storage system? More critical than performance, more interesting than power and cooling requirements, maybe even more important than price? Whether it's an enterprise-class All Flash Array, a new drive for your laptop or just a USB flash key, the first question … Continue reading All Flash Arrays: Where’s My Capacity? Effective, Usable and Raw Explained

Category: Storage for DBAs

All Flash Arrays: Can’t I Just Stick Some SSDs In My Disk Array?

In the previous post of this series I outlined three basic categories of All Flash Array (AFA): the hybrid AFA, the SSD-based AFA and the ground-up AFA. This post addresses the first one and is therefore aimed at answering one of the questions I hear most often: why can't I just stick a bunch of SSDs … Continue reading All Flash Arrays: Can’t I Just Stick Some SSDs In My Disk Array?

All Flash Arrays: What Is An AFA?

For the last couple of years I've been writing a series of blog posts introducing the concepts of flash-memory and solid state storage to those who aren't part of the storage industry. I've covered storage fundamentals, some of what I consider to be the enduring myths of storage, a section of unashamed disk-bashing and then … Continue reading All Flash Arrays: What Is An AFA?

Understanding Flash: Summary – NAND Flash Is A Royal Pain In The …

NAND flash is a genuinely difficult storage medium – it wears out, has slow erases, and requires complex management. This article summarises the Understanding Flash series and explains why architecture is what separates great all-flash arrays from merely fast ones.

Understanding Flash: Fabrication, Shrinkage and the Next Big Thing

NAND flash manufacturers have been shrinking transistors for decades, but 2D planar NAND is hitting its physical limits. This article explains process geometries, 3D NAND as the answer, and why new memory technologies face a billion-dollar barrier to market.

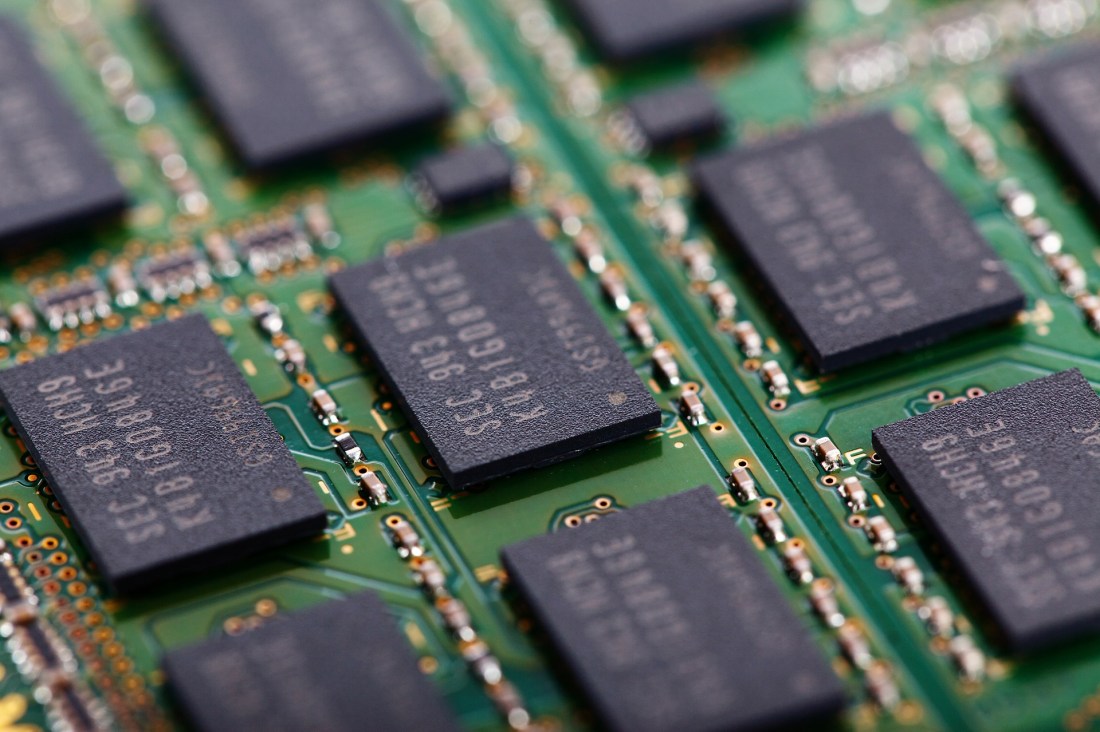

Understanding Flash: Floating Gates and Wear

NAND flash wears out because repeated program and erase operations degrade the oxide layer in floating gate transistors. This article explains how flash cells store data and why wear affects SLC, MLC and TLC differently.

Understanding Flash: Unpredictable Write Performance

Not all NAND flash writes are equal. MLC flash has fast pages and slow pages, creating unpredictable write latency unless the storage controller manages them intelligently. This article explains why write performance varies and what enterprise arrays do about it.

Understanding Flash: The Write Cliff

When flash garbage collection cannot keep pace with incoming writes, performance falls off a cliff. This article explains background versus active garbage collection, write amplification and why predictability matters more than peak speed.

Understanding Flash: Garbage Collection Matters

NAND flash can only be erased at the block level, not the page level. Garbage collection is the process that recycles stale pages to keep a flash system writable – and without it, performance collapses. This article explains why.

Understanding Flash: The Flash Translation Layer

The flash translation layer is the hidden software layer that makes NAND flash usable as enterprise storage. This article explains logical block mapping, wear levelling, garbage collection and write amplification.