This month sees the four year anniversary of some interesting events. Commonwealth countries around the world celebrated the Diamond Jubilee of Queen Elizabeth II. Whitney Houston was tragically found dead in a Beverly Hills hotel. The Caribbean was hit hard by sargassum seaweed invasion. And I made the decision to leave the comfort of Oracle databases and join the exciting … Continue reading Understanding Flash: The Fall and Rise of Flash Memory

Tag: Understanding Flash

Understanding Flash: What is 3D NAND?

3D NAND stacks flash cells vertically rather than shrinking them further, overcoming the physical limits of 2D planar NAND. This article explains how V-NAND and charge trap flash work and why they matter for enterprise storage.

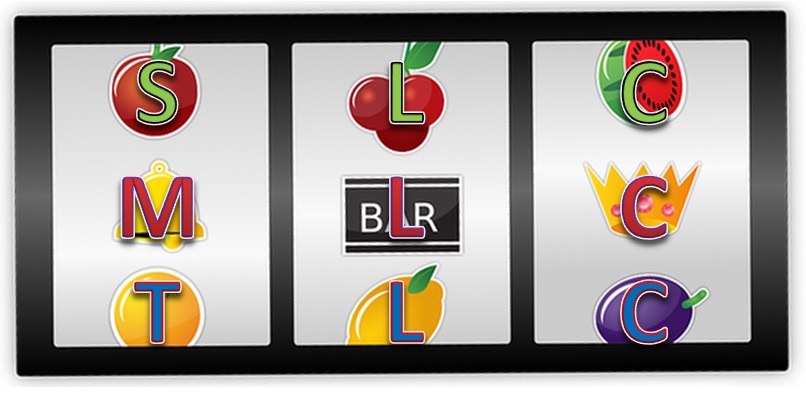

Understanding Flash: Summary – NAND Flash Is A Royal Pain In The …

NAND flash is a genuinely difficult storage medium – it wears out, has slow erases, and requires complex management. This article summarises the Understanding Flash series and explains why architecture is what separates great all-flash arrays from merely fast ones.

Understanding Flash: Fabrication, Shrinkage and the Next Big Thing

NAND flash manufacturers have been shrinking transistors for decades, but 2D planar NAND is hitting its physical limits. This article explains process geometries, 3D NAND as the answer, and why new memory technologies face a billion-dollar barrier to market.

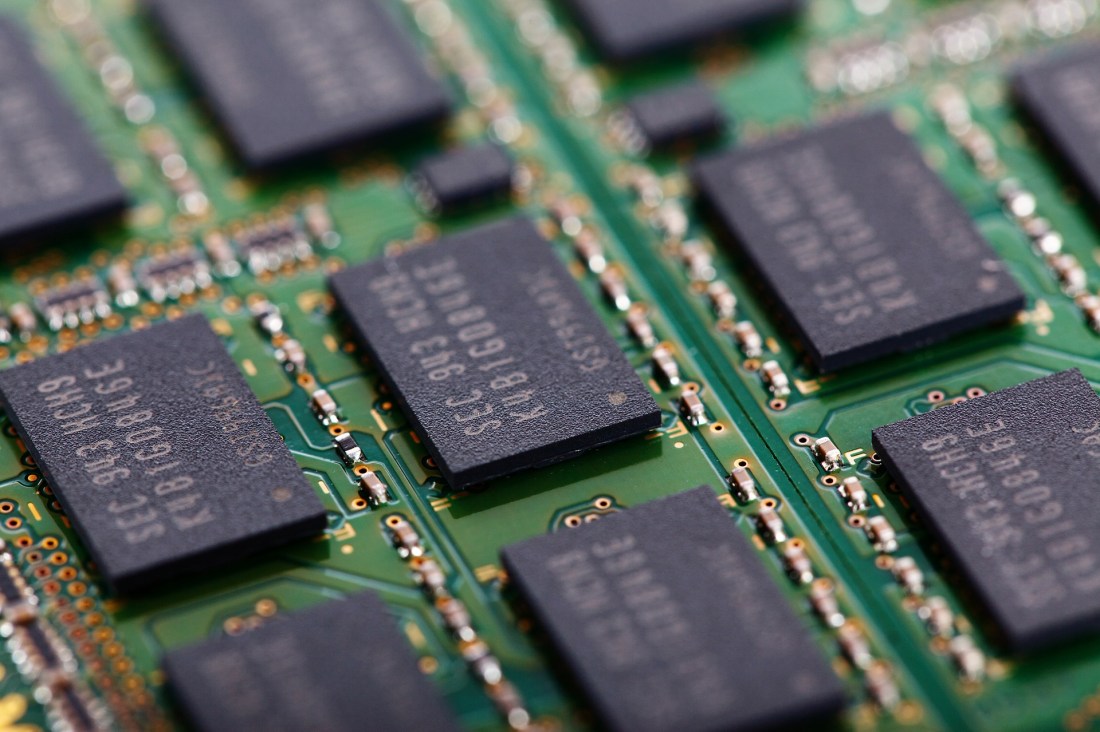

Understanding Flash: Floating Gates and Wear

NAND flash wears out because repeated program and erase operations degrade the oxide layer in floating gate transistors. This article explains how flash cells store data and why wear affects SLC, MLC and TLC differently.

Understanding Flash: Unpredictable Write Performance

Not all NAND flash writes are equal. MLC flash has fast pages and slow pages, creating unpredictable write latency unless the storage controller manages them intelligently. This article explains why write performance varies and what enterprise arrays do about it.

Understanding Flash: The Write Cliff

When flash garbage collection cannot keep pace with incoming writes, performance falls off a cliff. This article explains background versus active garbage collection, write amplification and why predictability matters more than peak speed.

Understanding Flash: Garbage Collection Matters

NAND flash can only be erased at the block level, not the page level. Garbage collection is the process that recycles stale pages to keep a flash system writable – and without it, performance collapses. This article explains why.

Understanding Flash: The Flash Translation Layer

The flash translation layer is the hidden software layer that makes NAND flash usable as enterprise storage. This article explains logical block mapping, wear levelling, garbage collection and write amplification.

Understanding Flash: SLC, MLC and TLC

SLC, MLC and TLC NAND flash differ in how many bits each cell stores. More bits per cell means lower cost and higher density – but slower performance and reduced endurance. This article explains the trade-offs for enterprise storage.